- · 《电子设计工程》栏目设[06/03]

- · 《电子设计工程》数据库[06/03]

- · 《电子设计工程》收稿方[06/03]

- · 《电子设计工程》投稿方[06/03]

- · 《电子设计工程》征稿要[06/03]

- · 《电子设计工程》刊物宗[06/03]

深度报告:芯片设计EDA 2.0时代,三大路径搞定六

作者:网站采编关键词:

摘要:EDA是Electronic Design Automation的缩写,几十年来成为芯片设计模块、工具、流程的代称。从仿真、综合到版图,从前端到后端,从模拟到数字再到混合设计,以及工艺制造等,EDA工具涵盖了

EDA是Electronic Design Automation的缩写,几十年来成为芯片设计模块、工具、流程的代称。从仿真、综合到版图,从前端到后端,从模拟到数字再到混合设计,以及工艺制造等,EDA工具涵盖了芯片设计、布线、验证和仿真等所有方面。

芯片的制造十分受制于EDA工具和设计流程,EDA的发展速度近十多年来越来越跟不上芯片设计规模和需求的快速增长。如何基于新的技术和平台,参考其它软件行业的发展过程,

推动EDA工具和设计流程进入新的时代是当今芯片制造中一个容易被忽视的关键环节。

在2021世界半导体大会暨南京国际半导体博览会的第二天,国产EDA智能软件和系统创企芯华章针对芯片解决设计难、人才少、设计周期长、设计成本高企的问题,发布了《EDA 2.0白皮书》。芯华章科技董事长兼CEO王礼宾相信,智能化的EDA 2.0时代,会使设计芯片像开发程序那样简单,制造芯片像搭积木那样灵活。

本期的智能内参,我们推荐芯华章的报告《EDA2.0白皮书》, 从EDA1.0的发展历程、现阶段问题与挑战分析,给出芯片EDA2.0未来发展的三大路径。

本期内参来源:芯华章

原标题:

《EDA2.0白皮书》

作者: 未注明

一、EDA历史与挑战

1、EDA发展史

芯片设计工具了计算机辅助设计 (Computer-Aided Design, CAD)、计算机辅助工(Computer-Aided Engineering, CAE)和EDA (Electronic Design Automation)三个阶段。

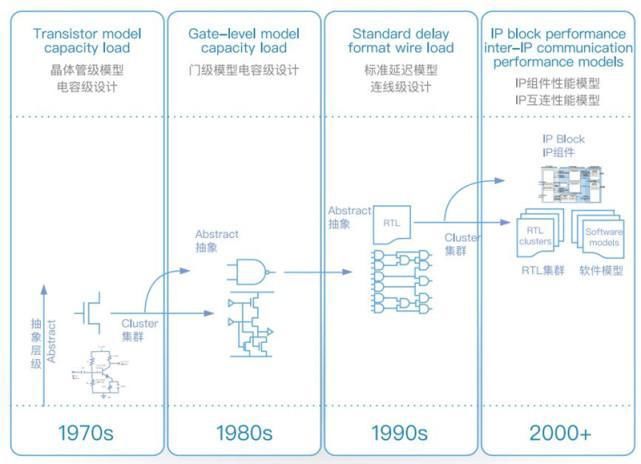

早期集成电路设计是纯手动描绘版图,第一个突破是1970年代CAD/CAE的诞生,也就是我们说的计算机辅助设计。基于计算机的电子设计工具出现,相对于手工设计方法而言是一个更大的改进,但工程师们仍然花费了不必要的时间在连接芯片时使用大量节点。之后晶体管集群被抽象为门级电路,提升了设计的抽象层次,但是设计仍然要在电压和电容级别去分析。

第二个突破发生于1990年代,EDA技术的诞生让工程师可以用硬件描述语言描述设计,可以通过仿真在流片前提前验证,并且在提高设计效率的同时,大大减少芯片制造环节的风险。之后基于IP模块的设计也逐渐成为EDA产业的一部分,IP厂商通过提供成熟的IP复用,与EDA工具一起支持客户的复杂芯片设计。这个过程中硬件芯片设计的抽象层级不断提高。

▲芯片描述抽象层级的提高

▲芯片描述抽象层级的提高

进入21世纪,微电子技术取得了突飞猛进的发展,以HDL语言描述、系统级仿真和综合技术为特点、以自动化设计为目标的EDA工具逐渐出现,并发展为今天这样面向专用集成电路(ASIC)的设计流程。

目前我们正在使用的EDA设计制造流程都是基于2000年左右开始形成的基础,可以称之为“EDA1.0” 。之后20多年EDA的发展,都是在1.0上逐渐增加各种内容,比如基于FPGA的验证、低功耗设计、工艺改进带来的各种可靠性验证、远程服务器运行EDA工具、基于IP组件的设计复用,等等。

这些叠加式的改进基于EDA1.0,不断提升EDA设计的效率,但是从抽象层级、设计方法学角度看,没有出现很大的改变,可以认为一直到今天我们都还处于“EDA1.x”的发展过程中。

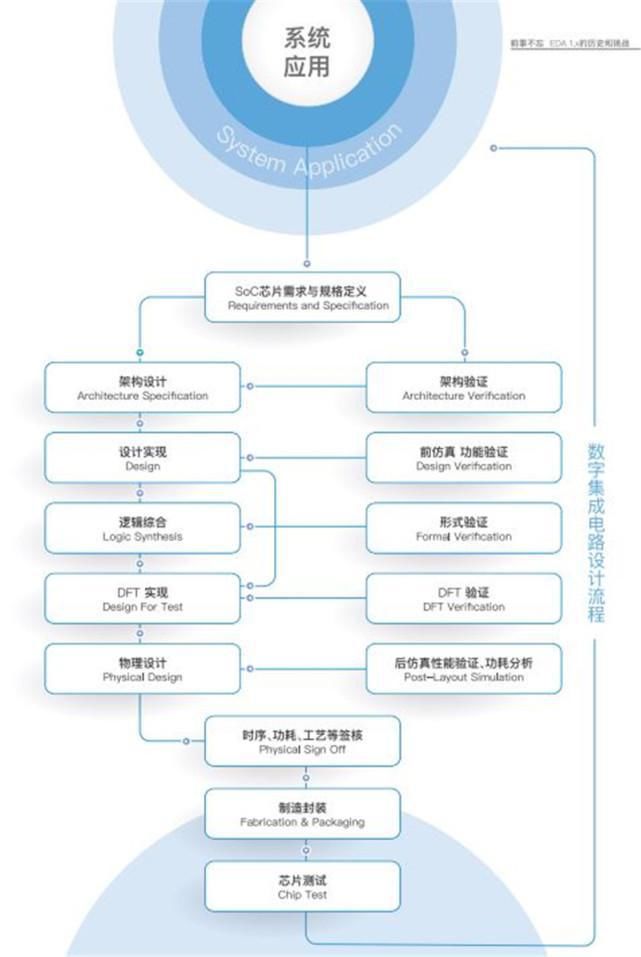

▲数字集成电路设计流程

▲数字集成电路设计流程

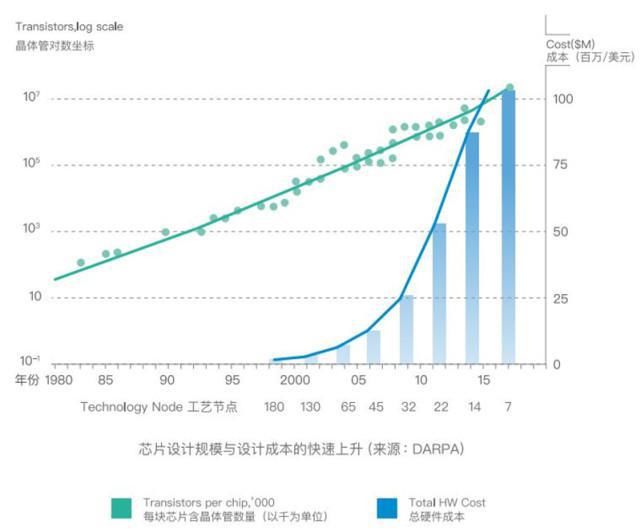

2、新时代EDA新要求

EDA 1.x的发展在过去30年间,一直都支撑着芯片设计从几千颗晶体管到现在百亿级晶体管的集成度, 但近年来随着制造工艺、面积功耗、接口引脚数量等限制条件逐渐逼向极限,通用处理器的综合性能提高越来越缓慢,而AI、云服务器、智能汽车、5G、工业智能控制等不同应用领域对半导体芯片的性能要求越来越高,功耗、成本的要求越来越分化,芯片设计、验证的成本也随之急速上升,设计制造周期也难以压缩。

▲芯片设计规模与设计成本的快速上升

▲芯片设计规模与设计成本的快速上升

以谷歌公司为例,作为一家软件、算法、系统和云平台厂商,我们看到它近年来在TPU、编解码等自主设计的芯片,甚至AI对EDA设计的辅助上都有很大投入。下一步谷歌还会将自己这些创新集成到自研处理器芯片,形成“谷歌硬件平台”。类似的,Nvidia公司在2019年收购的Mellanox,其长远目标也 是将Mellanox公司所创新的SmartNIC功能模块集成进自己的新一代SoC处理器。同样,亚马逊、微软、华为、阿里巴巴等云厂商,也都已经或布局了自己的SoC芯片产品和研发团队。

未来的系统产品创新和竞争都会紧密围绕定制芯片展开,在一颗芯片或封装内的完整系统才有最优化的性能和功耗,再加上与软件系统的紧密配合,会给系统产品厂商带来最大的竞争优势,这里另一个典型的例子就是芯片、硬件系统、操作系统直到应用系统全面开花的苹果公司。

文章来源:《电子设计工程》 网址: http://www.dzsjgc.cn/zonghexinwen/2021/0613/1362.html